# Digital Logic Design I (SS3023)

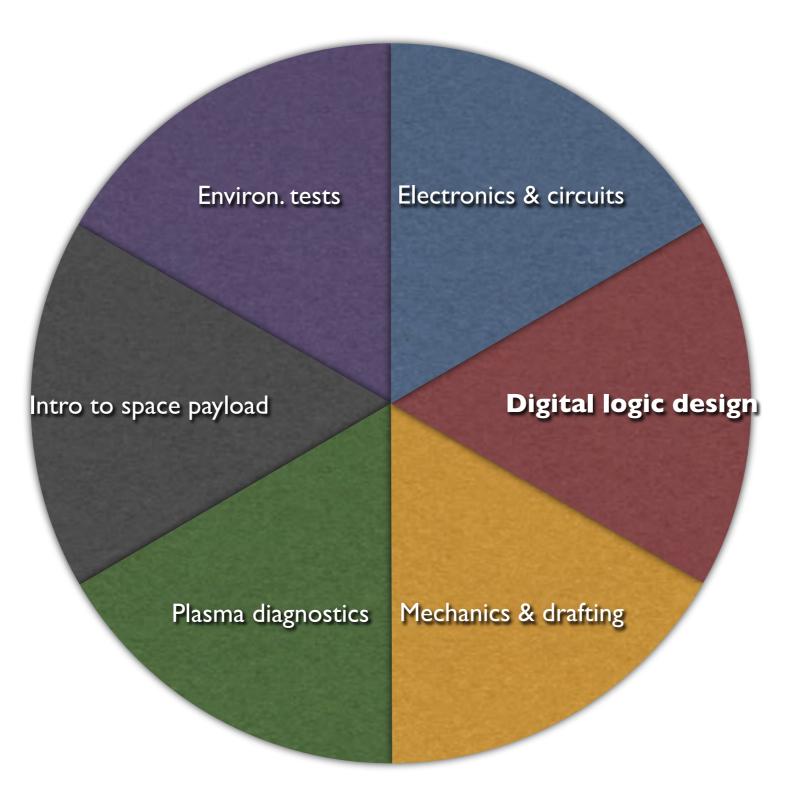

### **Course Overview**

Instructor: Chi-Kuang Chao

Department of Space Science and Engineering

National Central University

February 26, 2021

## Syllabus

- Instructor: Chi-Kuang Chao

- Course type: elective course

- Classrooms: S4-805 electrical shop

- Lecture time: 3 hours/week

- Lecture hours: 10:00 12:50 (FRI)

## Objectives

- A comprehensive coverage of basic to advanced digital concepts with an emphasis on problem solving, troubleshooting, and applications.

- Fundamental knowledge to build space payload.

# Space payload

## Course outline

- Digital fundamentals

- Introductory concepts

- Number system, operations, and codes

- Logic gates

- Boolean algebra and logic simplification

- Combinational logic analysis

- Functions of combinational logic

- Latches, flip-flops, and timers

## Course outline (cont.)

- Digital fundamentals

- Counters

- Shift registers

- Memory and storage

- Programmable logic and software

- Signal interfacing and processing

- Computer concepts

- Integrated circuit technologies

## Course outline (cont.)

- Basic Verilog topics

- Overview of digital design with Verilog HDL

- Hierarchical modeling concepts

- Basic concepts

- Modules and ports

- Gate-level modeling

- Dataflow modeling

- Behavioral modeling

- Tasks and functions

- Useful modeling techniques

## Course outline (cont.)

- Advanced Verilog topics

- Timing and delays

- Switch-level modeling

- User-defined primitives

- Programming language interface

- Logic synthesis with Verilog HDL

- Advanced verification techniques

### Course materials

### Textbooks

Floyd, Thomas L., Digital Fundamentals, 10/E, Pearson Education, Inc., 2010. ISBN-10: 0-13-814646-2.

Palnitkar Samir, Verilog HDL: A Guide to Digital Design and Synthesis, 2nd ed., 2003.

## S4-805 electrical shop

- 5 x NI ELVIS, 5 x NI ELVIS II+, and IO x NI ELVIS III

- 10 x NI myRIO-1900

- I0 x Digilent ZYBO Zynq-7000

- 5 x NI USRP 2900

- I0 x ASUS Desktop PC

- I0 x anti-static pads

- PCB prototyping: circuit board plotter, through-hole conductivity/plating, multilayer prototyping, surface mount technology/finishing, screen printing and solder-resist masks, SMT solder paste printer, pick and place assembly system, and lead-free reflow oven.

## Devices for learning

### NI myRIO-1900

- NI LabVIEW Academic Site License Department Teaching License: Control and Embedded Systems Software Option

- Digilent ZYBO Zynq™-7000 Development Board

- Xilinx Vivado Design Suite: System Edition University Licenses

25 Licenses

## NI myRIO-1900

- Featuring NI industry-standard reconfigurable I/O (RIO) technology, the enclosed version of myRIO (myRIO-1900) places three I/O connectors, wireless capabilities, a dual-core ARM real-time processor, and a customizable Xilinx FPGA in the hands of students. With its onboard devices, seamless software experience, and library of courseware and tutorials, myRIO provides an affordable tool that helps students and educators "do real engineering" in one semester. Box contents

- Driver and software evaluation DVDs

- USB cable

- Power supply with international adapters

- I MXP protoboard accessory

- NI screwdriver and MSP screw-terminal connector

## NI myRIO starter accessory kit

- The NI myRIO starter accessory kit includes everything you need to get started connecting to and programming the I/O of NI myRIO. NI myRIO starter accessory kit contents:

- Barrel connector with leads

- Assorted capacitors

- Diodes

- 7-segment display

- Mechanical rotary encoder

- Photo interruptor (light sensor with LED)

- Assorted op-amps

- Assorted LEDs

- Small DC motor (I VDC to 3 VDC, no load speed: 6600 rpm)

# NI myRIO starter accessory kit (cont.)

- Microphone with audio jack

- MXP Breadboard Accessory

- Potentiometer (500 k $\Omega$ )

- Relay

- Assorted resistors

- Piezoelectric sensor

- Photocell

- 2 Hall effect sensors (latch and switch)

- Buzzer

- Assorted switches (DIP, slide, and rotary)

- Thermistor (NTC: 10 kΩ, 25 degrees)

- Assorted transistors

- Force sensing resistor

- Wire kit

# NI myRIO embedded systems accessory kit

- The NI myRIO embedded systems accessory kit contains common sensors, devices, and a display.

- Keypad

- Digital temperature sensor (I2C)

- Character LCD (I2C, SPI, and UART)

- Digital potentiometer (SPI)

- Bluetooth interface (UART)

- EEPROM (SPI)

- LED matrix

# Digilent ZYBO Zynq<sup>TM</sup>-7000 Development Board

The ZYBO (Zynq Board) is a feature-rich, ready-to-use, entrylevel embedded software and digital circuit development platform built around the smallest member of the Xilinx Zynq-7000 family, the Z-7010. The Z-7010 is based on the Xilinx All Programmable System-on-Chip (AP SoC) architecture, which tightly integrates a dual-core ARM Cortex-A9 processor with Xilinx 7-series Field Programmable Gate Array (FPGA) logic. When coupled with the rich set of multimedia and connectivity peripherals available on the ZYBO, the Zynq Z-7010 can host a whole system design. The on-board memories, video and audio I/O, dual-role USB, Ethernet and SD slot will have your design up-and-ready with no additional hardware needed.

## Z-7010

- 650Mhz dual-core Cortex-A9 processor

- DDR3 memory controller with 8 DMA channels

- High-bandwidth peripheral controllers: IG Ethernet, USB 2.0, SDIO

- Low-bandwidth peripheral controller: SPI, UART, I2C

- Reprogrammable logic equivalent to Artix-7 FPGA

- 28K logic cells

- 240KB Block RAM

- 80 DSP slices

- On-chip dual channel, I2-bit, I MSPS analog-to-digital converter (XADC)

## ZYBO

- ZYNQ XC7Z010-1CLG400C

- 512MB x32 DDR3 w/ 1050Mbps bandwidth

- Dual-role (Source/Sink) HDMI port

- 16-bits per pixel VGA output port

- Trimode (IGbit/I00Mbit/I0Mbit) Ethernet PHY

- MicroSD slot (supports Linux file system)

- OTG USB 2.0 PHY (supports host and device)

- External EEPROM (programmed with 48-bit globally unique EUI-48/64™ compatible identifier)

- Audio codec with headphone out, microphone and line in jacks

- I28Mb Serial Flash w/ QSPI interface

- On-board JTAG programming and UART to USB converter

- GPIO: 6 pushbuttons, 4 slide switches, 5 LEDs

- Six Pmod connectors (I processor-dedicated, I dual analog/digital)

#### Quote(Taiwan) 179130

Print Date: 2015-01-09 15:58:44

國家發展儀器股份有限公司

台北市大安區敦化南路二段216號12樓

TEL: 02-2377-2222 FAX: 02-2377-7676

新竹縣竹北市自強南路8號14樓之3

TEL: 03-657-6222 FAX: 03-657-6066

FAX: 07-537-5111(高雄辦事處)

Contact ID: **75873** Zip Code: 320

Name: 趙吉光 Payment: Net30

Company: 國立中央大學 太空科學研究所 Quote Date: 2015-Jan-9

Address: 桃園縣 中壢市 五權里2鄰中大路300號 科學 Quoted By: 曹 斯皓

四館805室-1

Tel: 886-03-422-7151-65754/65781 Extension: 7145

Fax: 886-03-422-4394 Email: Szu-Hao.Tsao@ni.com

|   | Product PN | Description                                                                                       | Unit Price QTY.<br>[TWD] | Amount<br>[TWD] |

|---|------------|---------------------------------------------------------------------------------------------------|--------------------------|-----------------|

| 1 |            | NI MyRIO-1900 包含入門組合與嵌入式系統組合                                                                      | 33,333 1                 | 33,333          |

|   | One set of | includes the following items:                                                                     |                          |                 |

|   | 782692-01  | NI myRIO-1900. Includes WIFI and MSP Connector.                                                   | 1                        |                 |

|   | 783068-01  | NI myRIO Kits: Starter Kit Includes 5 MXP protoboard x5, Basic sensors, Battery holder, and parts | 1                        |                 |

|   | 783070-01  | NI myRIO Kits: Embedded Kit - Includes display, VGA/HDMI, audio codec                             | 1                        |                 |

**SUBTOTAL [TWD]:** 33,333

**VAT [TWD]:** 1,667

**TOTAL [TWD]:** 35,000

### 一元素科技股份有限公司

#### **E-Elements Technology Co., LTD**

公司地址

台北市內湖區瑞光路76巷61號5樓

TEL:(02) 2791-8139

統一編號

27729833

FAX:(02) 2792-6942

TO: 國立中央大學 太空科學研究所

ATTN: 趙吉光 老師

TEL: 03-4227151x65754

**FAX**: 03-4224394

OUR REF: ej2015010903

QUOTED BY: 林宗賢 Jason Lin

Mobile: 886-988810039

**Email**: jason.lin@e-elements.com.tw

DATE:

2015/1/9

#### **QUOTATION**

| Item | Vendor   | PART NUMBER                                     | Q'TY | UNIT/NTD\$ | TOTAL/NTD\$ | DELIVERY |

|------|----------|-------------------------------------------------|------|------------|-------------|----------|

| 1    | Digilent | ZYBO Zynq <sup>TM</sup> -7000 Development Board | 1    | \$5,200.00 | \$5,200.00  | 4weeks   |

1 本報價有效期限90天

2 付款條件:月結30天

3 以上報價已含稅及運費

#### 台幣匯款帳號 (TWD)

銀行名稱:台灣中小企銀-東湖分行

台幣銀行戶名:一元素科技股份有限公司

台幣匯款帳號:111-12-009101

## Resources provided by SPL

|         | myRIO-1900 | ZYBO<br>Zynq-7000 | LabVIEW for control & embedded systems software option      | Vivado<br>Design<br>Suite | Total      |

|---------|------------|-------------------|-------------------------------------------------------------|---------------------------|------------|

| 1 set   | NTD35,000  | NTD5,200          |                                                             | 0                         | NTD40,200  |

| 10 sets | NTD350,000 | NTD52,000         | NTD52,800 for<br>new option and<br>NTD16,200 for<br>renewal | 0                         | NTD418,200 |

# NCU undergraduate tuition for one semester

### 國立中央大學103學年度學雜費收費標準

| 一、學士班   |     |                              |                                 | 103年6月23                 | 日第596次行政會議通過                |

|---------|-----|------------------------------|---------------------------------|--------------------------|-----------------------------|

| 身份及費用別  | 院系所 | 工、資電學院<br>(含資管系、工管所、<br>藝研所) | 理、地科學院<br>( <mark>含生科系</mark> ) | 管理學院<br>(資管系 、工管所<br>除外) | 文、客家學院<br>(藝研所除外)、總<br>教學中心 |

|         | 學費  | 17, 490                      | 17, 490                         | 17, 330                  | 17, 330                     |

| 本籍生及99學 | 雜費  | 11, 170                      | 10, 950                         | 7, 540                   | 7, 180                      |

| 年度(含)以前 | 總計  | 28, 660                      | 28, 440                         | 24, 870                  | 24, 510                     |

| 入學之外籍生  | 學分費 | 1, 110                       | 1,110<br>(除數學系1,050)            | 1,020                    | 1,000                       |

|         | 學費  | 33, 181                      | 33, 505                         | 29, 037                  | 28, 785                     |

| 100學年度起 | 雜費  | 19, 487                      | 19, 678                         | 17, 054                  | 16, 906                     |

| 入學之陸生及  | 總計  | 52, 668                      | 53, 183                         | 46, 091                  | 45, 691                     |

| 外籍生     | 學分費 | 2, 220                       | 2,220<br>(除數學系2,100)            | 2, 040                   | 2, 000                      |

Our cost: NTD40,200 > Your payment: NTD28,440

### **Features**

- Lecture a two-semester course in one semester. → Pre-study and self-learning are required.

- Use myRIO and ZYBO Zynq-7000 with industrial development tools, LabVIEW and Vivado, for intense practices during/after the courses. → Hand-on practices are extremely important. 12 practices will be used for grading.

- The ugly truth is resources are limited. For best practice, each student had better to use his/her own devices. → Only 10 students are allowed to participate this course. You shall pay great attentions on this course to get a pass.

## Grading

• 12 practices: 100%

## Evaluation

| Semester   | 2009/09 | 2010/03       | 2010/09 | 2011/03                      | 2011/09       | 2012/03        | 2012/09                      | 2013/03                          | 2013/09       | 2014/03       | 2014/09 | 2015/03                      |

|------------|---------|---------------|---------|------------------------------|---------------|----------------|------------------------------|----------------------------------|---------------|---------------|---------|------------------------------|

| Course     | N/A     | Circuits<br>I | N/A     | Circuits<br>II<br>(DLD I)    | Circuits<br>I | Circuits<br>II | Digital<br>Logic<br>Design I | Digital<br>Logic<br>Design<br>II | Circuits<br>I | N/A           | N/A     | Digital<br>Logic<br>Design I |

| Students   | N/A     | 6             | N/A     | 21                           | 42            | 22             | 29                           | 11                               | 47            | N/A           | N/A     | 28→11                        |

| Failed     | N/A     | 0             | N/A     | 0                            | 0             | 14             | 0                            | ı                                | I             | N/A           | N/A     | 0                            |

| Evaluation | N/A     | 4.15          | N/A     | 4.38                         | 4.3           | 3.91           | 4.15                         | 4.19                             | 4.14          | N/A           | N/A     | 4.5 I                        |

| Semester   | 2015/09 | 2016/03       | 2016/09 | 2017/03                      | 2017/09       | 2018/03        | 2018/09                      | 2019/03                          | 2019/09       | 2020/03       | 2020/09 | 2021/03                      |

| Course     | N/A     | Circuits<br>I | N/A     | Digital<br>Logic<br>Design I | N/A           | Circuits<br>I  | N/A                          | Digital<br>Logic<br>Design I     | N/A           | Circuits<br>I | N/A     | Digital<br>Logic<br>Design I |

| Students   | N/A     | 7             | N/A     | 15→10                        | N/A           | 16→10          | N/A                          | 9                                | N/A           | 10            | N/A     |                              |

| Failed     | N/A     | 0             | N/A     | 0                            | N/A           | 0              | N/A                          | 0                                | N/A           | 0             | N/A     |                              |

| Evaluation | N/A     | 4.29          | N/A     | 4.24                         | N/A           | 4.91           | N/A                          | 4.9                              | N/A           | 4.9           | N/A     |                              |

# My courses

| Semester    | Undergraduate core<br>courses                                                    | Undergraduate selective courses                                                                      | Graduate selective courses                                           | Hours |

|-------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------|

| Fall 2018   | Engineering Laboratory (1/1) Introduction to Space Science and Engineering (1/2) |                                                                                                      | Space Environment and Exploration I (1/3) Plasma Measurement I (3/3) | 6     |

| Spring 2019 | <u>-</u>                                                                         | Hands-on Satellite System (2/2) Digital Logic Design I (3/3) Application and Practice of Space (2/2) | System (2/2) sign I (3/3) Practice of (3/3)                          |       |

| Fall 2019   | Engineering Laboratory (1/1) Introduction to Space Science and Engineering (1/2) | Space (2/2) Exploration and Practice of Exploration                                                  |                                                                      | 8     |

| Spring 2020 |                                                                                  | Hands-on Satellite System (2/2)<br>Circuits I (3/3)                                                  | Calibration and Test for Space Instruments II (3/3)                  | 8     |

| Week #                | 1st session                                        | 2nd session                                   | 3rd session          |  |  |

|-----------------------|----------------------------------------------------|-----------------------------------------------|----------------------|--|--|

| I (2/26)              | Course overview                                    | overview Selection test - from Chapter I to 6 |                      |  |  |

| 2 (3/5)               | Digital concepts Number system, operations, and co |                                               | Practice I           |  |  |

| 3 (3/12)              | Logic gates                                        | Boolean algebra and logic simplification      | Practice 2           |  |  |

| 4 (3/19)              | Combinational logic analysis                       | Functions of combinational logic              | Practice 3           |  |  |

| 5 (3/26)              | Latches, flip-flops, and timers                    | Counters                                      | Practice 4           |  |  |

| 6 (Spring break, 4/2) |                                                    | Break                                         |                      |  |  |

| 7 (4/9)               | Shift registers                                    | Memory and storage                            | Practice 5           |  |  |

| 8 (4/16)              | Programmable logic and software                    | Signal interfacing and processing             | Practice 6           |  |  |

| 9 (mid-term, 4/23)    |                                                    |                                               |                      |  |  |

| 10 (4/30)             | Computer concepts                                  | Integrated circuit technologies               | Practice 7           |  |  |

| 11 (5/7)              | Overview of digital design with Verilog HDL        | Hierarchical modeling concepts                | Practice 8           |  |  |

| 12 (5/14)             | Basic concepts                                     | Modules and ports                             | Practice 9           |  |  |

| 13 (5/21)             |                                                    | Gate-level modeling                           |                      |  |  |

| 14 (5/28)             | Dataflow m                                         | odeling                                       | Practice 10          |  |  |

| 15 (6/4)              | Behavioral modeling                                | Tasks and functions                           | Practice II          |  |  |

| 16 (6/11)             | Useful modeling techniques                         | Timing and delays                             | Practice 12          |  |  |

| 17 (6/18)             | Switch-level modeling.                             | User-defined primitives.                      | Programming language |  |  |

| 18 (final, 6/25)      |                                                    | Break                                         |                      |  |  |

### For more information

- Please visit the course web page at <a href="http://athena.ss.ncu.edu.tw/">http://athena.ss.ncu.edu.tw/</a>

- Contact me

- By phone: 03-4227151

- Ext.65754 at S4-804 (Office)

- Ext.65781 at S4-805-1 (Core facilities)

- Ext.36755 at S4-820 (Learning facilities)

- By e-mail: <a href="mailto:ckchao@jupiter.ss.ncu.edu.tw">ckchao@jupiter.ss.ncu.edu.tw</a>