# 數位邏輯設計

Verilog

2021.05.14

#### Module

Module:基本組成單元

語法協定:

每行結束後需有分號,表示敘述完畢。

單行註解://註解

多行註解:/\*註解\*/

數字規格: <size>'<base format><number>

ex: 4'b1111 4bit 二進位數 = 1111 16'd255 16bit 十進位數 = 255 //base format default為十進位

module module\_name (輸出入埠 型態 名稱, 輸出入埠 型態 名稱);//需與硬體連接之輸出入埠

參數定義; //無需與硬體連接之輸出入埠 參數初值設定;

電路功能 敘述;//每個敘述如果大於兩行,用begin end連接

endmodule

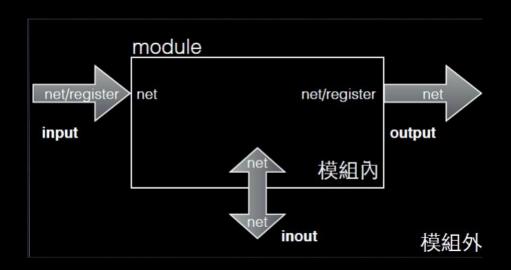

#### Input/Output

- 接線方向

- Input: wire only

- Output : reg /wire

- Inout : wire only

#### Wire/Register

- 接線型態

- 接線(Net): wire 用於連接硬體

- 暫存器(Register): reg 資料儲存空間,也可以如接線 般交流

- 參數(Parameter):parameter,設定定值

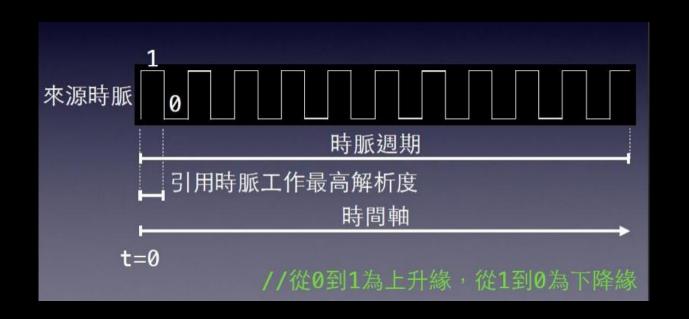

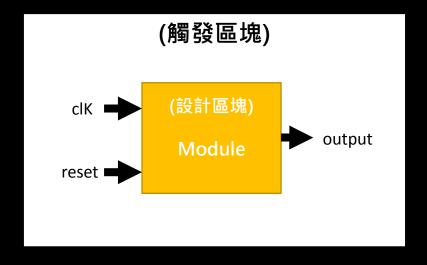

#### Clock

• 在硬體語言中,所有的依據都是以硬體引入的時脈(clock)做為來源的依據。

#### 條件判斷

```

• If –else

if(<expression>) <begin>

<statement_or_null>

<end>

else if(<expression>)

<begin>

<statement or null>

<end>

else <begin>

<statement or null>

<end>

```

#### case

```

case(<expression>)

Case1: <begin>

<statement or null>

<end>

Case2:(<expression>) <begin>

<statement or null>

<end>

Default: <begin>

<statement or null>

<end>

endcase

```

## 練習(除頻)

```

module clock_divide( input clk, // 屬性為wire, 為預設 (預設為1MHz時脈)

output reg clk2 // 需指定值,使用暫存器

);

reg [19:0] cnt; // 不需連接模組外之參數, 不用輸出入埠

//初值設定

initial begin

clk2 = 1'b0;

cnt = 20'b0;

end

//創造一秒的時脈

always @(posedge clk)begin //觸發條件

if (cnt == 999999) cnt <= 0; //counter數到99999把其歸0,表示1MHz去數一秒的總數

else cnt <= cnt+1;</pre>

end

always @(posedge clk)begin

if (cnt <= 499999) clk2 <= 0; //duty cycle 50%

else clk2 <= 1; //1MHz的計數器數1000000所以在一半的地方做反相

end

//判斷上能用 <= ,就不要用 <

endmodule

```

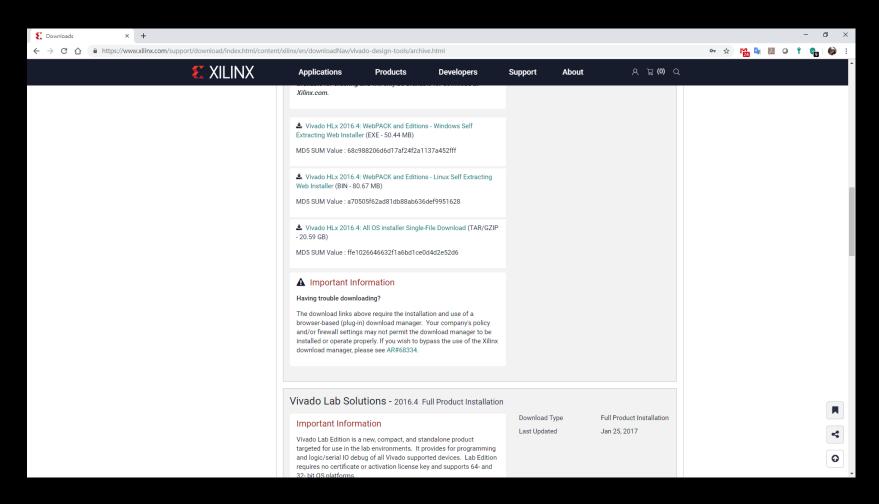

# VIVADO

#### Installing Vivado and Digilent Board Files

• Vivado 設計套件,是 FPGA 廠商 Xilinx (賽 靈思)公司 2012 年發布的集成設計環境,幫助實現 FPGA 整合與開發。(前身為ISE)

• Digilent Board Files 為 Vivado設計環境提供 Digilent 板卡訊息幫助快速實現板卡整合。

#### Vivado 設計套件

- Vivado 為 RTL 設計提供了一個合成,整合和驗證除錯的工作環境。

- Vivado 軟體包含

- IP Integrator:用於設計嵌入式處理器系統的硬體部分。 您可以指定 ARM Cortex-A9 處理器內核,IP 周邊及這些 組件的互連及其相應的詳細配置。

- Software Development Kit: SDK 是一個集成的開發環境,與 Vivado 互補,用於 C / C ++ 嵌入式軟體應用程序創建和驗證。 SDK 是基於 Eclipse 開源框架所構建的。

- Vivado 邏輯分析儀:分析&除錯硬體設計。

#### 到 Xilinx website 下載WebPack版本

https://www.xilinx.com/support/download.html

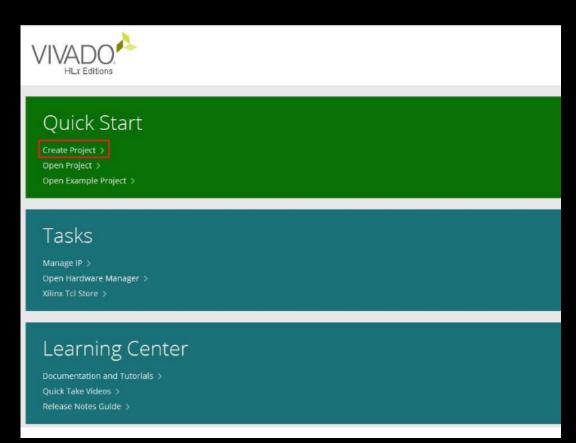

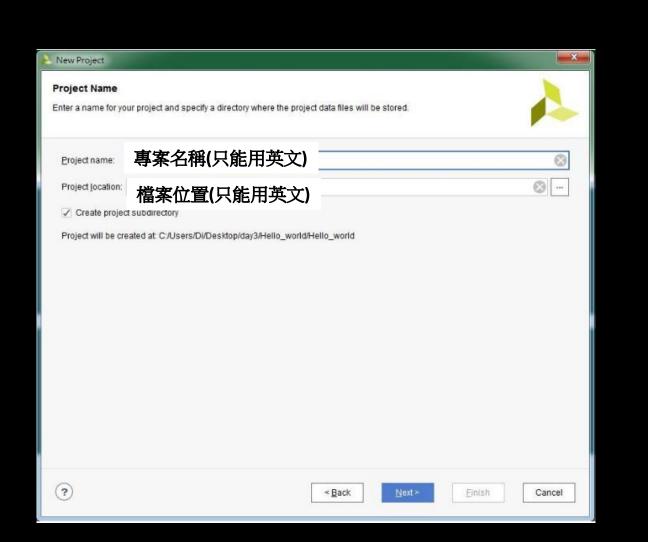

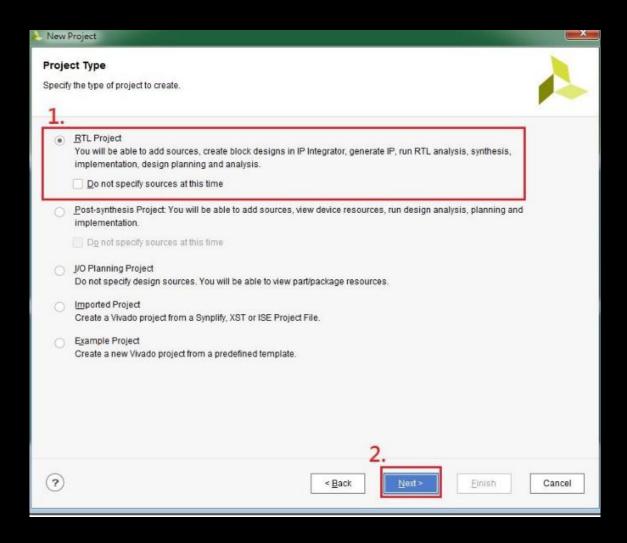

# 開啟專案

RTL: Register Transfer Level,是一種對同步數位電路的抽象模型,這種模型是根據數位訊號在硬體暫存器、存儲器、組合邏輯裝置和匯流排等邏輯單元之間的流動,以及其邏輯代數運作方式來確定的。(from 維基百科)

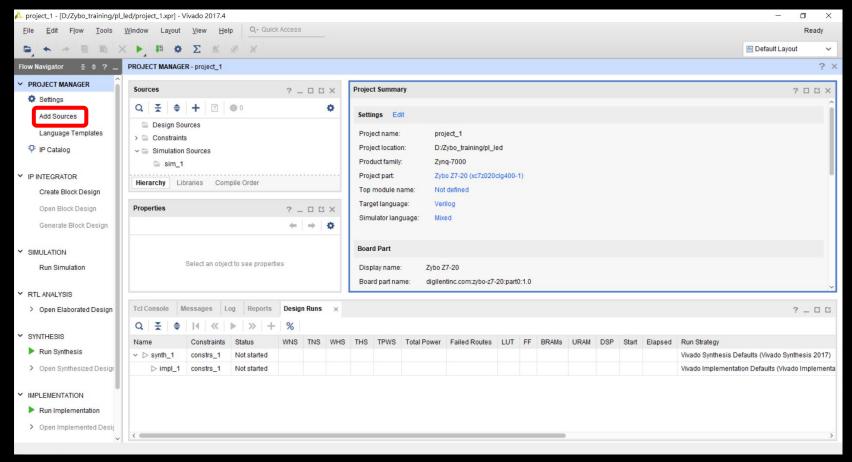

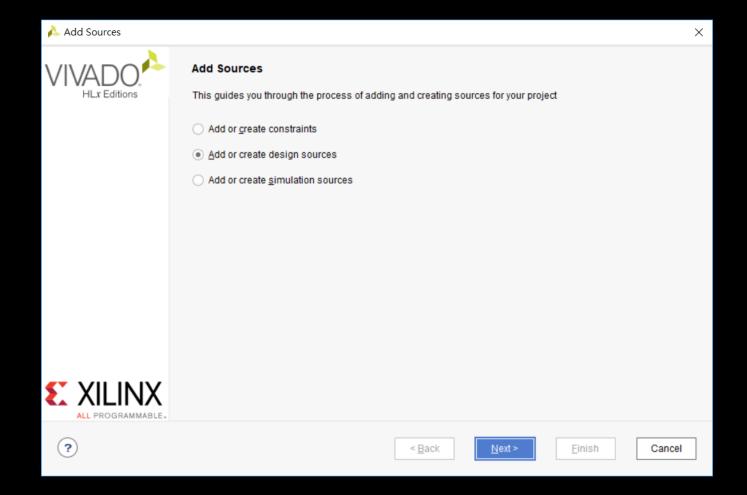

## 添加與撰寫 Verilog 程式

Project Manager -> Add sources 增加檔案

#### 新增設計

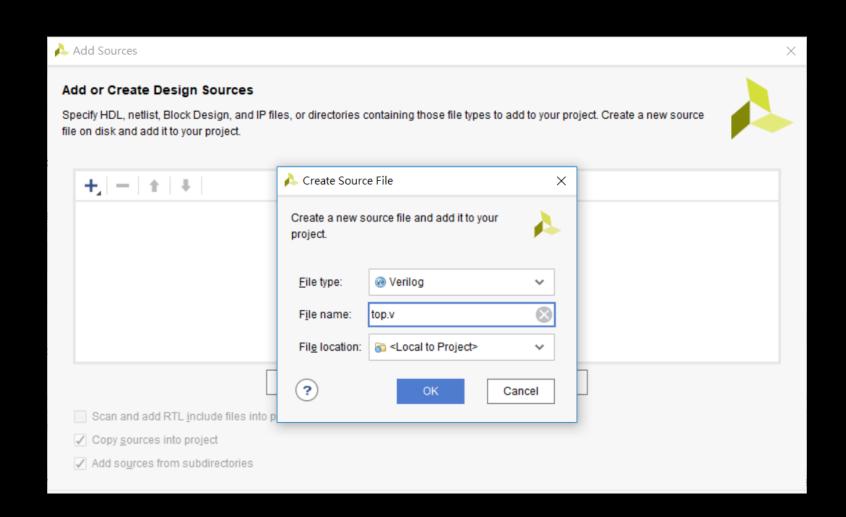

## Create File 新增 top.v 主程式

#### Test Bench

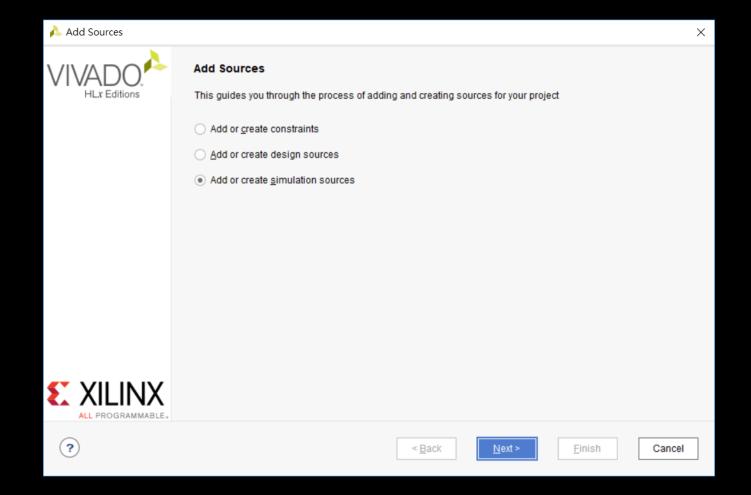

#### 設定模擬

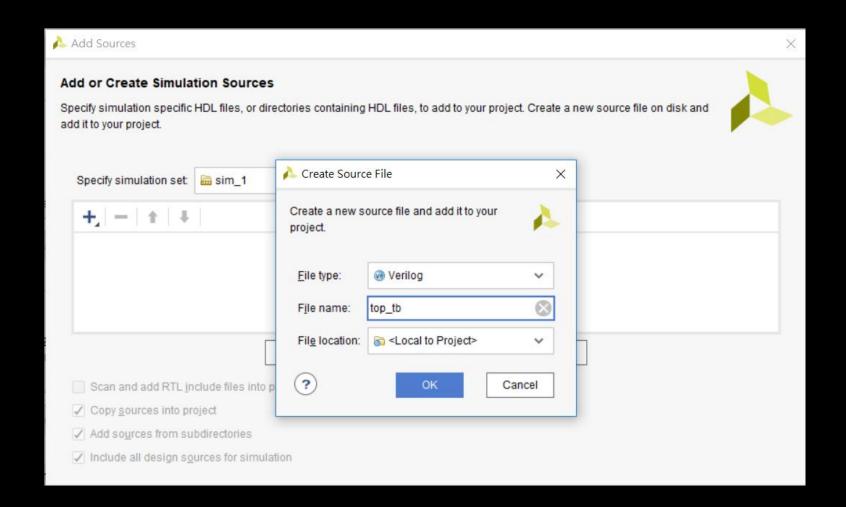

## 設定模擬:Create file

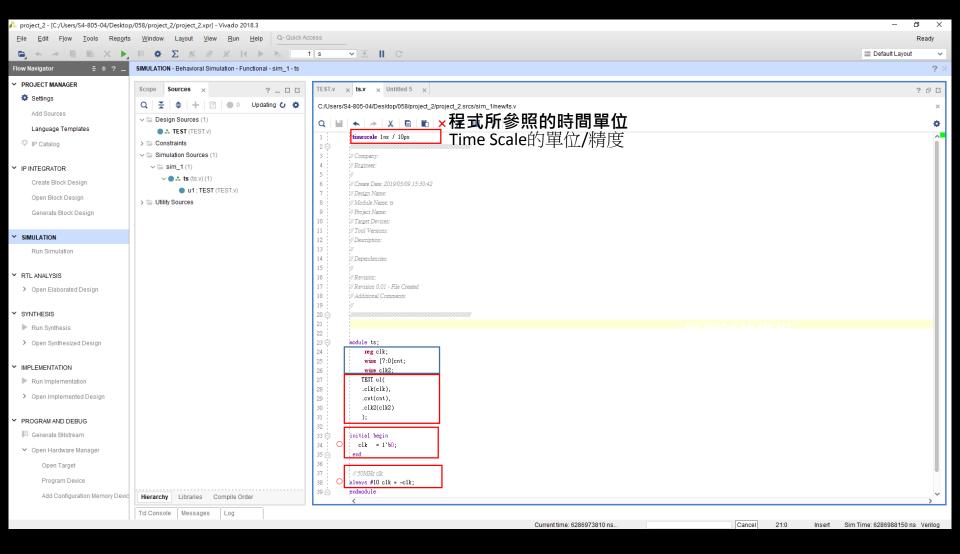

#### 設定模擬:完成 test bench

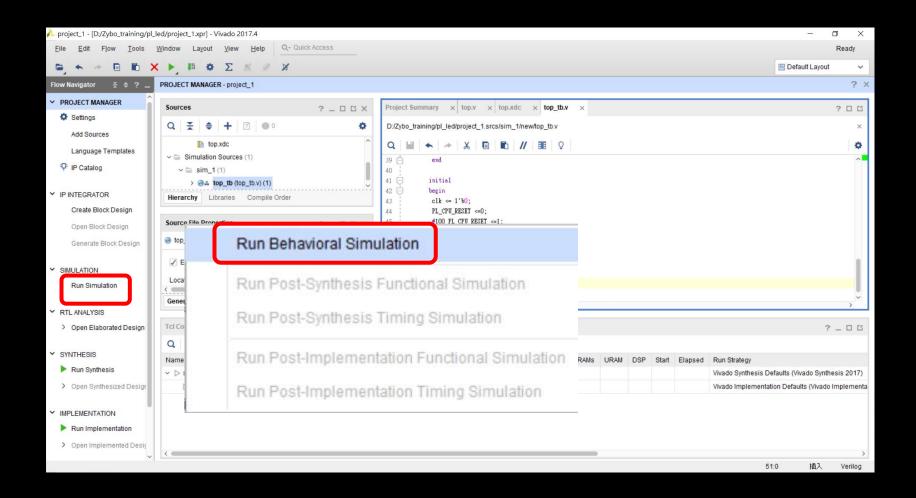

#### 設定模擬: Run Simulation

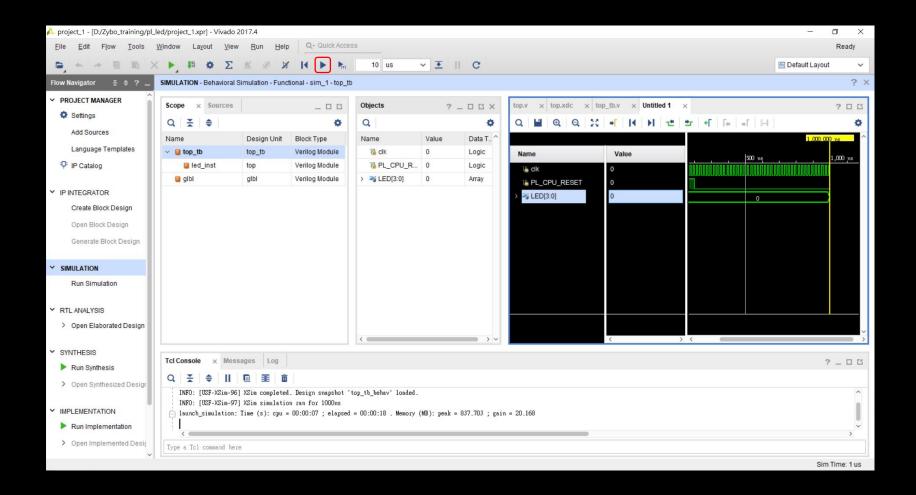

#### 設定模擬: Simulation result

#### 作業

• If clk=50Mhz, how to generate clk2=10 hz?

• If clk=100Mhz, how to generate clk2=50M hz?

#### 作業

- 完成兩題除頻的模擬

- 將結果截圖,並加入解釋

- 5/28 10:00 前,以PDF 寄到 信箱 gain514@g.ncu.edu.tw

- 郵件主旨 數位邏輯設計\_你的名字